Un multiplexeur est un circuit combinatoire qui possède 2nlignes d'entrée et une seule ligne de sortie. Simplement, le multiplexeur est un circuit combinatoire à entrées multiples et à sortie unique. Les informations binaires sont reçues des lignes d'entrée et dirigées vers la ligne de sortie. Sur la base des valeurs des lignes de sélection, une de ces entrées de données sera connectée à la sortie.

Contrairement au codeur et au décodeur, il y a n lignes de sélection et 2nlignes d'entrée. Il y a donc au total 2Ncombinaisons possibles d’entrées. Un multiplexeur est également traité comme Mux .

Il existe différents types de multiplexeurs qui sont les suivants :

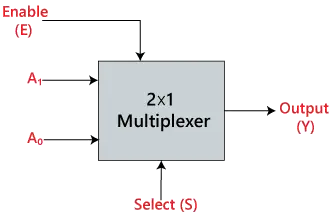

Multiplexeur 2×1 :

Dans un multiplexeur 2 × 1, il n'y a que deux entrées, c'est-à-dire A0et un1, 1 ligne de sélection, soit S0et des sorties uniques, c'est-à-dire Y. Sur la base de la combinaison des entrées présentes sur la ligne de sélection S0, une de ces 2 entrées sera connectée à la sortie. Le schéma fonctionnel et la table de vérité des 2 × 1 multiplexeur sont donnés ci-dessous.

Diagramme:

Table de vérité:

L'expression logique du terme Y est la suivante :

O=S0'.UN0+S0.UN1

Le circuit logique de l’expression ci-dessus est donné ci-dessous :

Multiplexeur 4×1 :

Dans le multiplexeur 4×1, il y a un total de quatre entrées, soit A0, UN1, UN2, et A3, 2 lignes de sélection, soit S0et S1et une sortie unique, c'est-à-dire Y. Sur la base de la combinaison des entrées présentes au niveau des lignes de sélection S0et S1, une de ces 4 entrées est connectée à la sortie. Le schéma fonctionnel et la table de vérité des 4 × 1 multiplexeur sont donnés ci-dessous.

Diagramme:

Table de vérité:

L'expression logique du terme Y est la suivante :

O=S1'S0' UN0+S1'S0UN1+S1S0' UN2+S1S0UN3

Le circuit logique de l’expression ci-dessus est donné ci-dessous :

Multiplexeur 8 à 1

Dans le multiplexeur 8 vers 1, il y a au total huit entrées, c'est-à-dire A0, UN1, UN2, UN3, UN4, UN5, UN6, et A7, 3 lignes de sélection, soit S0, S1et S2et une sortie unique, c'est-à-dire Y. Sur la base de la combinaison des entrées présentes au niveau des lignes de sélection S0, S1,et S2, une de ces 8 entrées est connectée à la sortie. Le schéma fonctionnel et la table de vérité des 8 × 1 multiplexeur sont donnés ci-dessous.

Diagramme:

Table de vérité:

L'expression logique du terme Y est la suivante :

O=S0'.S1'.S2'.UN0+S0.S1'.S2'.UN1+S0'.S1.S2'.UN2+S0.S1.S2'.UN3+S0'.S1'.S2UN4+S0.S1'.S2UN5+S0'.S1.S2.UN6+S0.S1.S3.UN7

Le circuit logique de l’expression ci-dessus est donné ci-dessous :

Multiplexeur 8 × 1 utilisant un multiplexeur 4 × 1 et 2 × 1

Nous pouvons mettre en œuvre le 8 × 1 multiplexeur utilisant un multiplexeur d'ordre inférieur. Pour mettre en œuvre le 8 × 1 multiplexeur, il nous en faut deux 4 × 1 multiplexeurs et un 2 × 1 multiplexeur. Le 4 × 1 multiplexeur possède 2 lignes de sélection, 4 entrées et 1 sortie. Les deux × 1 multiplexeur n'a qu'une seule ligne de sélection.

Pour obtenir 8 entrées de données, nous avons besoin de deux 4 × 1 multiplexeurs. Le 4 × 1 multiplexeur produit une sortie. Donc, pour obtenir le résultat final, nous avons besoin d'un 2 × 1 multiplexeur. Le schéma fonctionnel de 8 × 1 multiplexeur utilisant 4 × 1 et 2 × 1 multiplexeur est donné ci-dessous.

Multiplexeur 16 à 1

Dans le multiplexeur 16 vers 1, il y a au total 16 entrées, soit A0, UN1, …, UN16, 4 lignes de sélection, soit S0, S1, S2, et S3et une sortie unique, c'est-à-dire Y. Sur la base de la combinaison des entrées présentes au niveau des lignes de sélection S0, S1, et S2, une de ces 16 entrées sera connectée à la sortie. Le schéma fonctionnel et la table de vérité des 16 × 1

Diagramme:

Table de vérité:

L'expression logique du terme Y est la suivante :

Y=A0.S0'.S1'.S2'.S3'+A1.S0'.S1'.S2'.S3+A2.S0'.S1'.S2.S3'+A3.S0'.S1'.S2.S3+A4.S0'.S1.S2'.S3'+A5.S0'.S1.S2'.S3+A6.S1.S2.S3'+A7.S0'.S1.S2.S3+A8.S0.S1'.S2'.S3'+A9.S0.S1'.S2'.S3+Y10.S0.S1'.S2.S3'+A11.S0.S1'.S2.S3+A12S0.S1.S2'.S3'+A13.S0.S1.S2'.S3+A14.S0.S1.S2.S3'+A15.S0.S1.S2'.S3Le circuit logique de l’expression ci-dessus est donné ci-dessous :

Multiplexeur 16 × 1 utilisant un multiplexeur 8 × 1 et 2 × 1

Nous pouvons mettre en œuvre le 16 × 1 multiplexeur utilisant un multiplexeur d'ordre inférieur. Pour mettre en œuvre le 8 × 1 multiplexeur, il nous en faut deux 8 × 1 multiplexeurs et un 2 × 1 multiplexeur. Le 8 × 1 multiplexeur possède 3 lignes de sélection, 4 entrées et 1 sortie. Les deux × 1 multiplexeur n'a qu'une seule ligne de sélection.

Pour obtenir 16 entrées de données, nous avons besoin de deux multiplexeurs 8 × 1. Le 8 × 1 multiplexeur produit une sortie. Donc, pour obtenir le résultat final, nous avons besoin d'un 2 × 1 multiplexeur. Le schéma fonctionnel de 16 × 1 multiplexeur utilisant 8 × 1 et 2 × 1 multiplexeur est donné ci-dessous.